As the global semiconductor industry prepares for the upcoming GTC 2026, scheduled for March 15 in San Jose, California, market attention is sharply focused on the next wave of AI chip innovation. Hosted by NVIDIA, GTC is widely regarded as a global barometer for AI development trends. CEO Jensen Huang recently hinted at “unprecedented technological breakthroughs,” fueling expectations that NVIDIA will unveil its revolutionary AI processor, widely rumored to be the “Feynman” chip.

Industry analysts predict that this new AI processor will be the world’s first to leverage TSMC’s cutting-edge A16 (1.6nm) process technology. Although TSMC’s roadmap indicates that A16 mass production will begin in the second half of 2026, wafer shipments for NVIDIA are expected around 2028, with large-scale customer deliveries potentially extending into 2029–2030.

Dual-Site Manufacturing Strategy: Taiwan and the United States

To meet NVIDIA’s projected demand for next-generation AI silicon, TSMC is accelerating fab expansion in both Kaohsiung, Taiwan, and Arizona, United States. Initial production is expected to ramp up in Taiwan, where process maturity and yield optimization can be achieved efficiently. Once trial production stabilizes, part of the capacity will transition to the U.S. to align with American strategic manufacturing requirements.

Notably, the completion of TSMC’s third Fab 21 (P3) phase in Arizona will mark the most advanced semiconductor manufacturing facility in the United States, helping diversify geographic risk and ease concerns over concentrated advanced chip production in Taiwan.

A16 (1.6nm): Back-Side Power Supply Innovation

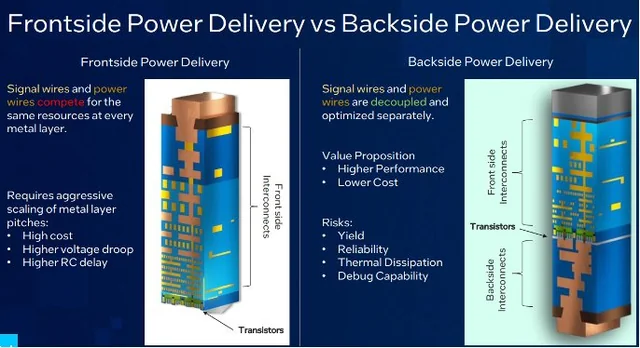

The A16 process represents more than simple transistor miniaturization from 2nm (A20). Its defining breakthrough lies in “back-side power delivery.” Unlike traditional chip designs—where multiple metal interconnect layers are stacked above transistors—A16 relocates the power supply network to the back of the wafer.

This architectural shift reduces signal interference, alleviates routing congestion, and enhances overall performance efficiency. As transistor density increases, conventional front-side metal routing creates severe bottlenecks. Back-side power supply effectively separates signal and power pathways, improving both speed and energy efficiency.

AI Chips, Silicon Photonics, and CPO: From Copper to Optical

Market expectations extend beyond core processors. NVIDIA is also anticipated to reveal advancements in silicon photonics and Co-Packaged Optics (CPO), transitioning high-speed data transmission from copper interconnects to optical architectures. This shift is critical for supporting exponential AI workload growth within hyperscale data centers.

For industry players like Lanao Communication Technology Limited, these developments signal a transformative era. As a provider of advanced optical and Ethernet transmission solutions, Lanao’s expertise in high-speed networking, data center interconnects, and sustainable communication technologies aligns directly with the AI infrastructure revolution. The transition to optical transmission and energy-efficient architectures reinforces the importance of scalable, high-bandwidth networking ecosystems.

Energy Efficiency: The Core of AI Sustainability

As AI models scale, power consumption becomes a structural constraint. TSMC’s A16 back-side power technology is designed not only to boost performance but also to significantly reduce energy loss. With global grids already under pressure, energy-efficient chip design is essential to maintaining sustainable AI growth.

By combining advanced manufacturing innovation with cross-regional capacity expansion, TSMC and NVIDIA are effectively launching a two-pronged strategy—technological leadership and geopolitical balance. The upcoming GTC 2026 may well mark a pivotal milestone in redefining AI computing performance, supply chain resilience, and the future of global semiconductor ecosystems.

By Oliver

Hi, I'm Oliver, Marketing Specialist at lanaotek.com.

I specialize in translating cutting-edge optical and Ethernet transmission technologies into clear, valuable insights that help our customers stay ahead in a fast-evolving digital world.

By turning complex technical concepts into practical, business-driven content, I aim to empower decision-makers with the knowledge they need to make confident, future-ready choices.

Internet Data Center

Internet Data Center FAQs

FAQs Industry News

Industry News About Us

About Us Data Center Switch

Data Center Switch  Enterprise Switch

Enterprise Switch  Industrial Switch

Industrial Switch  Access Switch

Access Switch  Integrated Network

Integrated Network  Optical Module & Cable

Optical Module & Cable

Call us on:

Call us on:  Email Us:

Email Us:  2106B, #3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.

2106B, #3D, Cloud Park Phase 1, Bantian, Longgang, Shenzhen, 518129, P.R.C.